## Introduction to Computers and Programming

Prof. I. K. Lundqvist

Reading: B pp. 505-507, Machine language handout

Lecture 7 Sept 16 2003

Recap – Computer Architecture

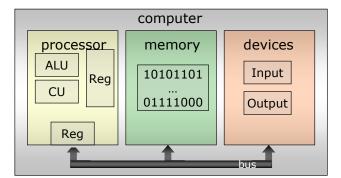

Computer Organization

- The von Neumann architecture

- Same storage device for both instructions and data

- The von Neumann Bottleneck

#### Stored Program

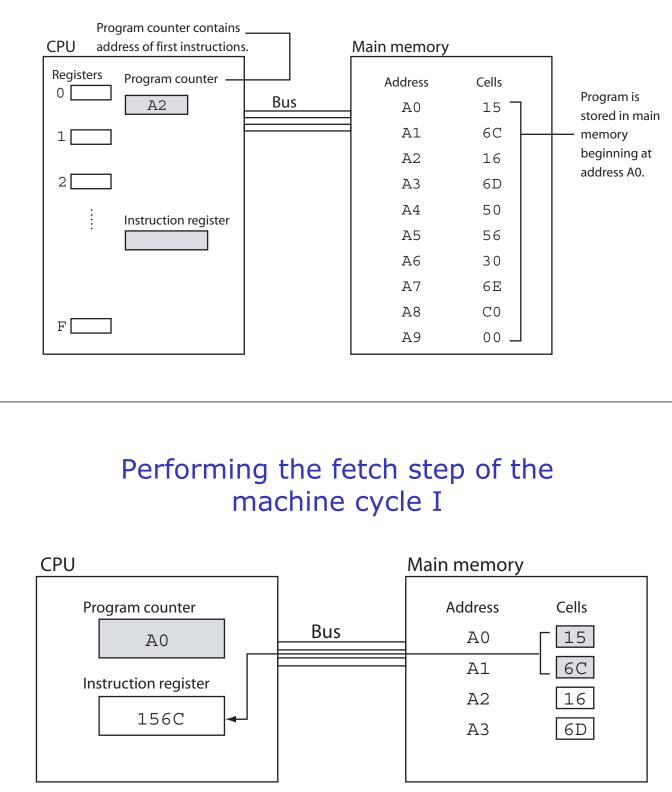

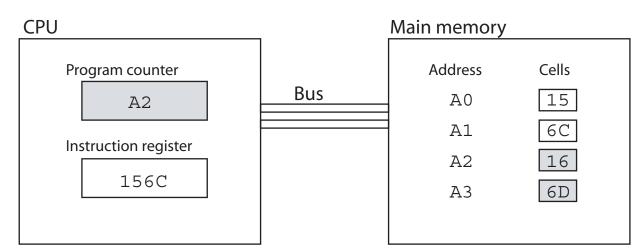

1. At the beginning of the fetch step the instruction starting at address A0 is retrieved from memory and placed in the instruction register.

# Performing the fetch step of the machine cycle II

2. Then the program counter is incremented so that it points to the next instruction.

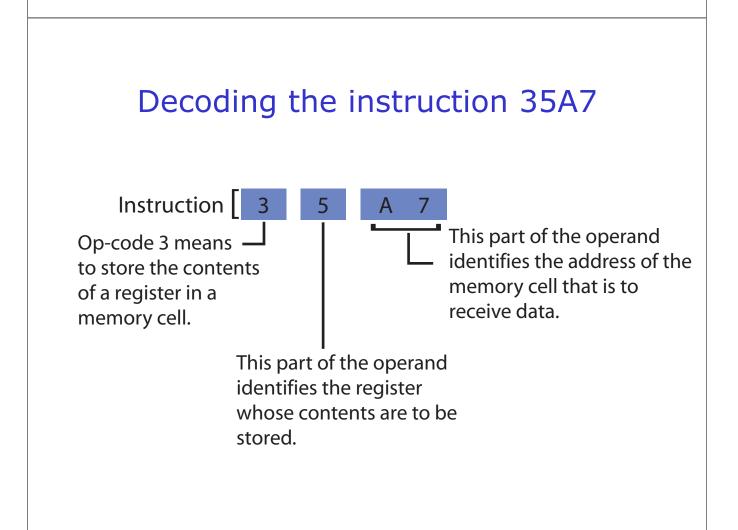

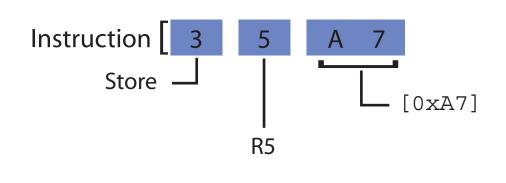

## **Mnemonics**

- It is hard to remember many numbers

- Use words associated with the numbers

store R5, [0xA7] <=> 35A7

| db                                        | org<br>direct store                                 | immediate<br>load<br>load reg, addr<br>indirect | direct load<br>load reg, [addr]           |

|-------------------------------------------|-----------------------------------------------------|-------------------------------------------------|-------------------------------------------|

| load reg, [reg]                           | store reg, [addr]                                   | store reg, [reg]                                | MOVE<br>move reg1, reg2                   |

| integer<br>addition<br>addi reg, reg, reg | floating<br>point<br>addition<br>addf reg, reg, reg | bitwise OR<br>or reg, reg, reg                  | bitwise AND<br>and reg, reg, reg          |

| bitwise XOR<br>xor reg, reg, reg          | rotate right<br>ror reg, num                        | <b>jmp</b><br>jmp addr                          | jmpLE<br><sub>jmpLE</sub><br>reg<=R0,addr |

| jmpEQ<br><sub>jmpEQ</sub><br>reg=R0,adr   | halt                                                |                                                 |                                           |

#### Assembly Language I

- *immediate load* load reg, number

load reg, label

- direct load

load reg, [adr]

- indirect load

load reg1, [reg2]

- *direct store* **store** reg, [adr]

- *indirect store* store reg1, [reg2]

- unconditional jump jmp adr

- origin

org adr

- *data byte* db dataitem

jmp Start org 0x30;Start: load R0, 0x10; load R1, [R0]; Program that switches the load R2, [new number]; contents in Store R1, [new number]; memory location Store R2, [R0]; 0x20 and 0x10 halt; org 0x20; new number : **db** 10d org 0x10; old number : **db** 25d;

# CQ I

1. Both Contain 0

2. Oxfe contains 0,0xff contains 04

3. Oxfe contains 0, 0xff contains 05

4. I don't know

### Assembly II

bitwise or

or reg1, reg2, reg3

- bitwise and and reg1, reg2, reg3

- bitwise exclusive or

xor reg1, reg2, reg3

|                                | <b>load</b> R1, 00100110b; |  |  |

|--------------------------------|----------------------------|--|--|

|                                | <b>load</b> R2, 11111111b; |  |  |

| Program to                     | <b>load</b> R0, 0000000b;  |  |  |

| demonstrate the basic bit-wise | <pre>and R3,R1,R2;</pre>   |  |  |

| constructs                     | and R4,R1,R0;              |  |  |

|                                | or R5,R1, R2;              |  |  |

|                                | or R6, R1, R0;             |  |  |

|                                | <b>xor</b> R7,R1, R2;      |  |  |

|                                | halt;                      |  |  |

# CQ II

1. 1001

2.0000

3. 0110

4. I don't know